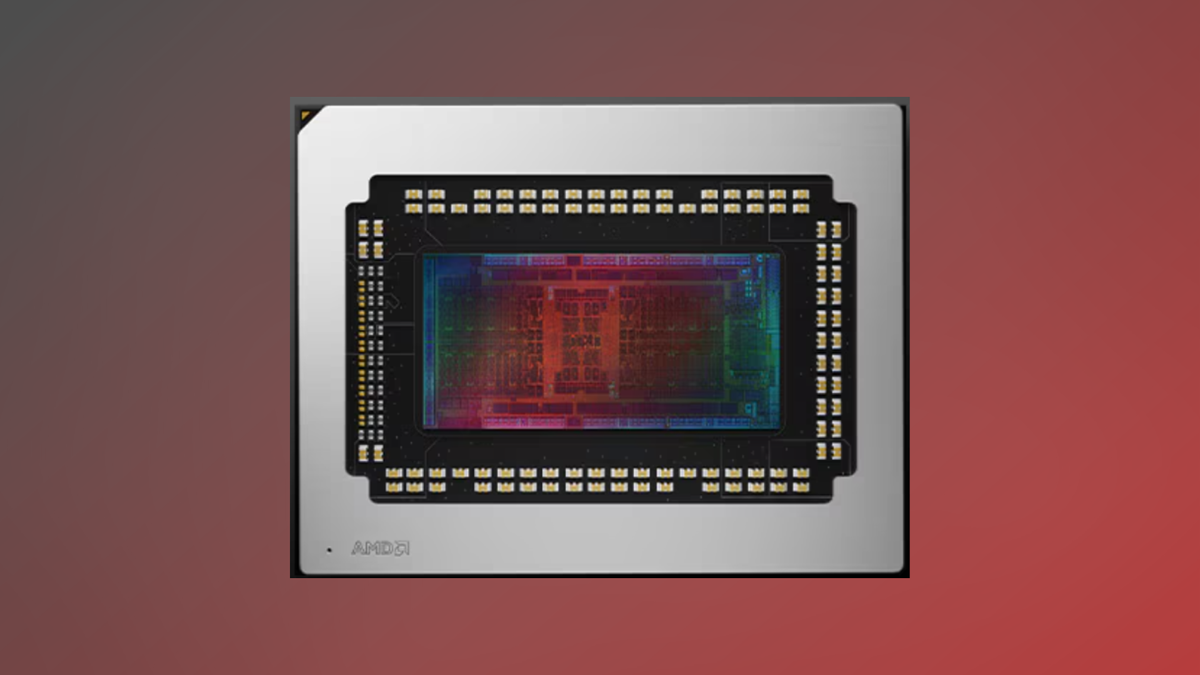

Chip War Heats Up: AMD's RDNA4 Navi 48 Packs Punch with Unprecedented Transistor Density

Breaking new ground in semiconductor technology, engineers have achieved a remarkable milestone: cramming an astounding 150 million transistors into every square millimeter of silicon. This groundbreaking advancement not only pushes the boundaries of miniaturization but also creates exciting possibilities for integrating advanced features like L3 cache directly on the processor die.

By packing transistors with such unprecedented density, chip designers are unlocking new potential for faster, more efficient computing architectures. The ability to incorporate L3 cache within the same silicon real estate means dramatically reduced data transfer latencies and improved overall processor performance.

This technological leap represents a significant step forward in the ongoing quest to make computing components smaller, more powerful, and increasingly sophisticated. As transistor density continues to increase, we can expect even more impressive computational capabilities in future generations of processors and electronic devices.